LEHRSTUHL FÜR BETRIEBSSYSTEME

Univ.-Prof. Dr. habil. Thomas Bemmerl

# Entwurf und Implementierung einer Virtualisierungsschicht für den Betriebssystemkern "MetalSVM"

## Design and Implementation of a Virtualization Layer for the Operating System Kernel "MetalSVM"

Jacek Galowicz Matrikelnummer: 285548

**Bachelorarbeit** an der Rheinisch-Westfälischen Technischen Hochschule Aachen Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Betriebssysteme

Betreuer: Dr. rer. nat. Stefan Lankes

# Contents

| Lis | t of                                                                       | Figures                                                                                                                                                                                                                                                                                                                  |                                         |                         | v                                                  |  |  |

|-----|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------|----------------------------------------------------|--|--|

| Lis | ist of Tables vii                                                          |                                                                                                                                                                                                                                                                                                                          |                                         |                         |                                                    |  |  |

| Lis | t of                                                                       | Listings                                                                                                                                                                                                                                                                                                                 |                                         |                         | ix                                                 |  |  |

| 1.  | Intro                                                                      | oduction                                                                                                                                                                                                                                                                                                                 |                                         |                         | 1                                                  |  |  |

| 2.  | Met                                                                        | alSVM on the Intel SCC                                                                                                                                                                                                                                                                                                   |                                         |                         | 3                                                  |  |  |

| 3.  | 3.1.<br>3.2.                                                               | ervisors in VirtualizationFull Virtualization Versus Paravirtualization                                                                                                                                                                                                                                                  | • •                                     | · · ·                   | 8<br>9<br>9<br>10<br>10                            |  |  |

|     | 3.3.                                                                       | Hypervisors in Linux                                                                                                                                                                                                                                                                                                     |                                         |                         | 10<br>11                                           |  |  |

| 4.  |                                                                            | ign and Implementation of the Hypervisor for MetalSVMHypervisor Initialization4.1.1. Loading the Switcher Pages4.1.2. Initializing Page Tables4.1.3. Creating /dev/lguest in the Filesystem4.1.4. Architecture-Specific Initialization                                                                                   | •                                       | · ·                     | 17<br>17<br>18                                     |  |  |

|     | <ul><li>4.2.</li><li>4.3.</li><li>4.4.</li><li>4.5.</li><li>4.6.</li></ul> | Guest Boot and paravirt_opsLguest LoaderHost-Guest Context SwitchSegments4.5.1. Special Segments for the Guest's Kernel Space4.5.2. Managing GDT Manipulation RequestsInterrupts4.6.1. Managing IDT Manipulation Requests4.6.2. Guest-Interrupt Handling in the Hypervisor4.6.3. Delivering Interrupts Back to the Guest | • · · · · · · · · · · · · · · · · · · · | · · ·<br>· · ·<br>· · · | 19<br>21<br>24<br>28<br>28<br>28<br>30<br>30<br>31 |  |  |

|     |                | 4.6.4.           | The Guest's Possibilities to Block Interrupts | 33 |  |  |

|-----|----------------|------------------|-----------------------------------------------|----|--|--|

|     |                | 4.6.5.           | Optimization: Direct Interrupt Delivery       | 35 |  |  |

|     |                | 4.6.6.           | Timer Supply                                  | 36 |  |  |

|     | 4.7.           | Shadov           | v Paging                                      | 38 |  |  |

|     | 4.8.           | Hypere           | ealls                                         | 42 |  |  |

|     |                | 4.8.1.           | How the Guest Casts a Hypercall               | 42 |  |  |

|     |                | 4.8.2.           | Processing Hypercalls in the Hypervisor       | 43 |  |  |

|     |                | 4.8.3.           | Asynchronous Hypercalls as an Optimization    | 43 |  |  |

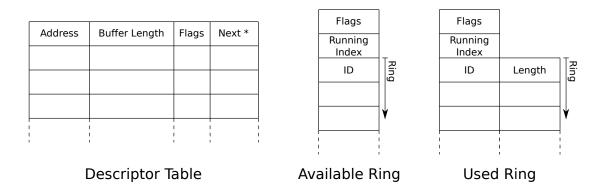

|     | 4.9.           | VirtIO           | Implementation                                | 44 |  |  |

|     |                | 4.9.1.           | The VirtIO Device Abstraction API             | 44 |  |  |

|     |                | 4.9.2.           | virtio_ring: Linux' Virtqueue Implementation  | 45 |  |  |

|     |                | 4.9.3.           | VirtIO in MetalSVM                            | 46 |  |  |

| E   | Eval           | uation           |                                               | 49 |  |  |

| э.  |                |                  | moment Details and Internation                | -  |  |  |

|     | 0.1.           |                  | rement Details and Interpretation             |    |  |  |

|     |                | 5.1.1.<br>5.1.2. | Host-Guest Context Switch                     |    |  |  |

|     |                | 5.1.2.<br>5.1.3. | Page Fault                                    |    |  |  |

|     |                | 5.1.5.<br>5.1.4. | System Calls                                  | 51 |  |  |

|     |                | 0.1.4.           |                                               | 51 |  |  |

| 6.  | Con            | clusion          |                                               | 53 |  |  |

| Α.  | Back           | kground          | d Knowledge                                   | 55 |  |  |

| B.  | Code           | e Listin         | gs                                            | 57 |  |  |

|     |                |                  |                                               |    |  |  |

| Bil | ibliography 63 |                  |                                               |    |  |  |

# **List of Figures**

| 1.1. | Establishing coherency domains                                  |

|------|-----------------------------------------------------------------|

| 2.1. | Schematic top view SCC block diagram                            |

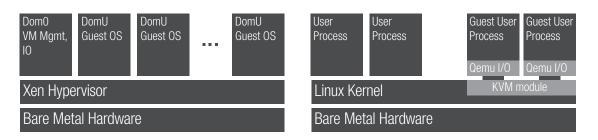

| 3.1. | The two different types of hypervisors                          |

| 3.2. | Privilege rings in the Intel x86 architecture                   |

| 3.3. | Structural differences between the Xen and KVM hypervisors 11   |

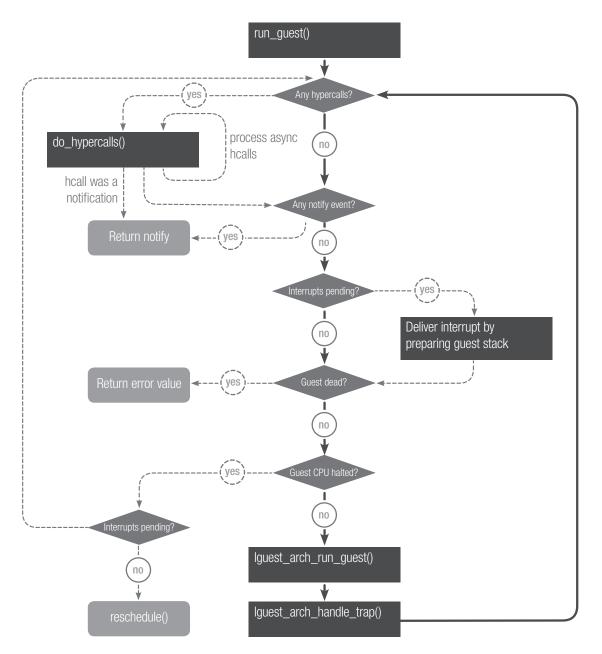

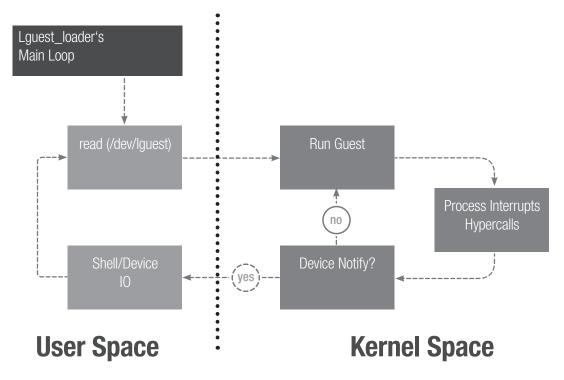

| 4.1. | Flow of lguest's main loop                                      |

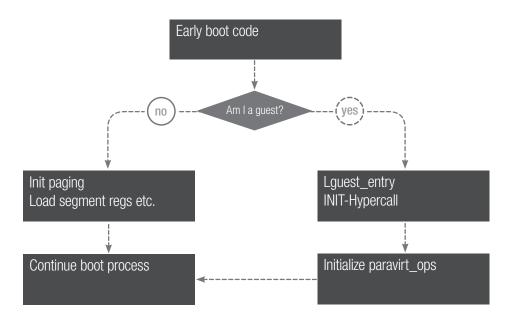

| 4.2. | Hypervisor-recognition at boot time                             |

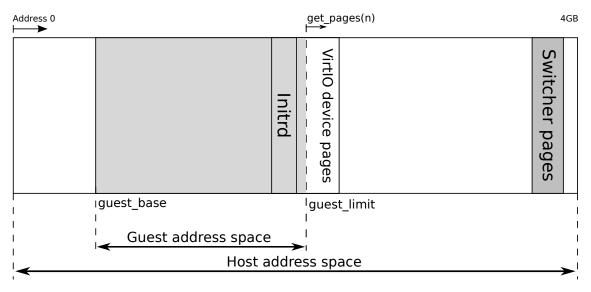

| 4.3. | Memory layout of host and guest                                 |

| 4.4. | Flow of lguest_loader's main loop                               |

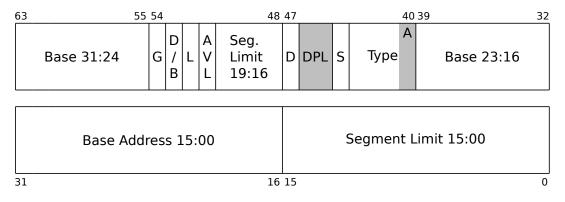

| 4.5. | Structure of a segment descriptor                               |

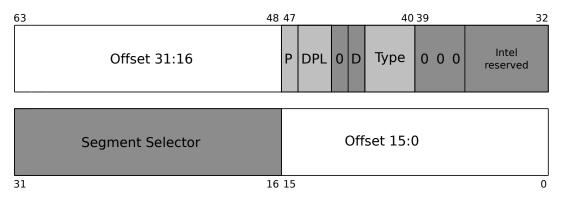

| 4.6. | Structure of an interrupt descriptor                            |

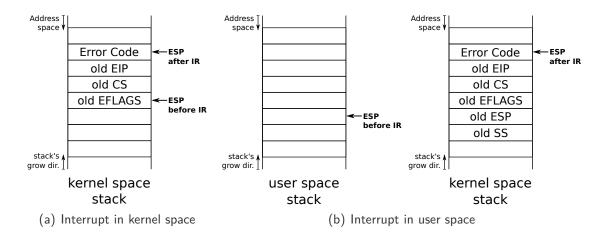

| 4.7. | Stack layouts before and after the occurence of an interrupt 33 |

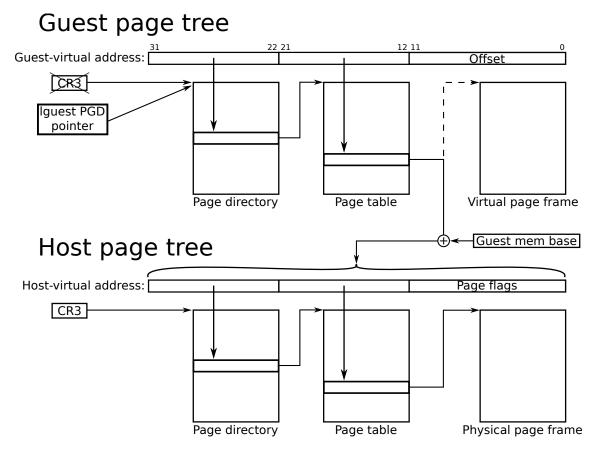

| 4.8. | Shadow paging mechanism explained                               |

| 4.9. | VirtIO ring structures 46                                       |

# List of Tables

| 3.1. | Comparison between full- and paravirtualization    |  | • |  |   | • | • | 7  |

|------|----------------------------------------------------|--|---|--|---|---|---|----|

| 4.1. | Lguest's main parts                                |  |   |  | • |   |   | 13 |

| 5.1. | Performance measurements taken in the guest system |  |   |  |   |   |   | 50 |

# List of Listings

| 4.1. | run_guest_once() procedure (metalsvm/drivers/lguest/x86/core.c) .        | 24 |

|------|--------------------------------------------------------------------------|----|

| 4.2. | Host-guest switcher code (metalsvm/drivers/lguest/x86/switcher_32.S)     | 26 |

| 4.3. | Definition of the lguest_pages structure and restoring the stack pointer |    |

|      | during guest-host context switch                                         | 27 |

| 4.4. | lguest_iret code (linux/arch/x86/lguest/i386_head.S)                     | 34 |

| 4.5. | copy_traps code (metalsvm/drivers/lguest/interrupts_and_traps.c) .       | 36 |

| 4.6. | Shadow paging code (metalsvm/drivers/lguest/pagetables.c)                | 41 |

| 4.7. | The virtqueue access function abstraction                                | 45 |

| B.1. | Lguest's main loop (metalsvm/drivers/lguest/lguest_core.c)               | 57 |

| B.2. | Linux' startup_32 routine (linux/arch/x86/kernel/head_32.S)              | 58 |

| B.3. | Linux' lguest_entry routine (linux/arch/x86/lguest/i386_head.S)          | 58 |

| B.4. | Linux' lguest_init routine (linux/arch/x86/lguest/boot.c)                | 59 |

| B.5. | modified timer_handler() code (metalsvm/arch/x86/kernel/timer.c) .       | 60 |

| B.6. | VirtIO structure definitions (metalsvm/include/virtio/virtio_ring.h) .   | 61 |

|      |                                                                          |    |

# 1. Introduction

In the last decades computer programmers were used to the fact that their old programs did automatically run faster when executed on new computer generations. This fact based on the condition of new computers' higher clock frequencies which allowed for executing more processor instructions within the same time. The growing clock frequencies also led to growing heat generation and power consuption which in turn became a problem for both laptop computers and bigger server farms.

As a reaction, the increase of processor frequency in new computers did nearly stagnate a few years ago, but so did not the increase of the number of cores: Even today's laptop computers have up to about ten of them. Programmers need to rewrite their programs to take advantage of this.

Such computer's hardware either implements the symmetric multiprocessing (SMP) or the message passing architecture. In SMP systems every core has an identical view to the system's memory space. This way the programmer only has to make sure that the calculations his program does are properly parallelizable. He does not have to care about which part of his parallelized program has to run on which core as the cores have an identical view onto the memory space. This paradigm is called *shared memory programming*. Since every core has its own cache, the hardware needs to provide a mechanism to keep shared memory consistent between the different caches. Commonly referred to as *cache coherence*, this mechanism involves serialization of memory access. With a growing number of cores, this also results in heavily growing demands to the memory-bandwidth.

Message passing computer systems solve this problem by providing every core with its private memory space and bus. However, having outpaced SMP systems in computer clusters in terms of prevalence, they are harder to program: Besides parallelizing, the programmer has to explicitly move the data between the core's memory spaces to where it is used. In the long term, microprocessor manufacturers seem to regard symmetric multiprocessing as a dead end.

When hardware of future generations will not provide an SMP-typical view on the system's memory, it will be a crucial task to achieve a shared memory environment with cache coherence by software. Although message passing applications scale very well, shared memory can be beneficial in situations with dynamically changing memory access patterns. Shared memory platforms are also easier to deal with when balancing the system load. This is where Intel's *Single-chip Cloud Computer* (SCC) joins research. The SCC is an experimental microprocessor prototype with 48 cores on its die (see Figure 2.1 on page 3) which do not support any cache coherence. It is built to study the possibilities of future generation many-core computer architectures. Most research is done in examining and demonstrating the use of the

#### 1. Introduction

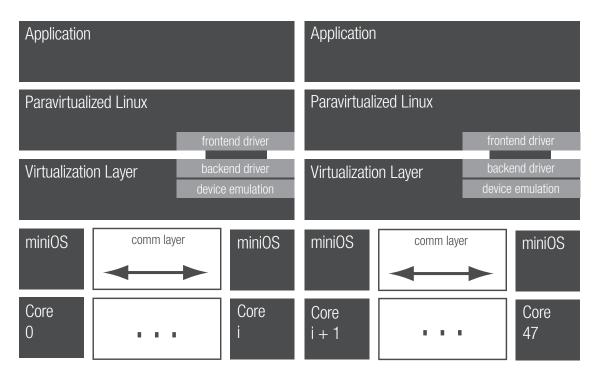

Figure 1.1.: Establishing coherency domains

SCC as a message passing architecture using the external and on-die memory for communication.

An attractive way of establishing a shared memory environment on this platform is adding a *virtualization layer* between message passing operating system kernels running on the cores and a single operating system kernel. The last-mentioned will find itself on a large virtual SMP computer system. This shall be achieved with a special small operating system running on each core providing the virtualization environment for an unmodified Linux kernel (see Figure 1.1). To enable the transparent use of a linear address space by the virtualized Linux kernel, the smaller kernels below the virtualization layer have to manage data exchange between the cores' different address spaces.

The focus of this thesis is implementing this virtualization layer in the operating system kernel MetalSVM, involving the port of an existing hypervisor implementation from the Linux kernel. This preliminary work allows later extension to a system managing coherency domains spanning over multiple cores. The thesis begins with describing MetalSVM and the Intel SCC together composing the target platform in Chapter 2. A general explanation about virtualization and virtualization mechanisms with focus on the Intel x86 architecture is given in Chapter 3. In this chapter the distinction between full- and paravirtualization is illustrated to point out the latter as most useful for the project and presents hypervisors in Linux which implement this approach. Finally, it explains the choice of which hypervisor to port to MetalSVM. Chapter 4 gives very detailed insights into the actual implementation.

# 2. MetalSVM on the Intel SCC

MetalSVM is a small monolithic operating system kernel. Initially it shared the largest part of its codebase with *EduOS*, a very basic operating system kernel developed for educational purposes. Both EduOS and MetalSVM have been developed at the Chair for Operating Systems of RWTH Aachen University since 2010. The name "MetalSVM" is a mix of the term *bare metal* and the abbreviation *SVM* standing for "Shared Virtual Memory".

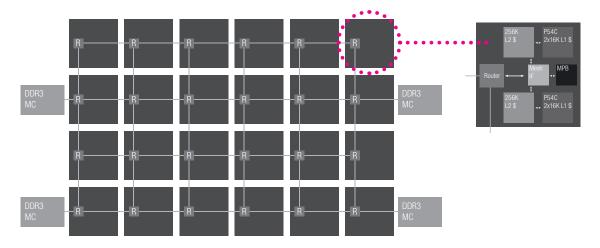

The SCC's 48 P54C cores are arranged pairwise on  $6 \times 4$  tiles on the microchip's die. Each of them is equipped with each 16 kB L1 data and instruction cache as well as 256 kB L2 cache. Up to 64 GB of external memory are provided by four memory controllers surrounding the grid. Due to the architecture's 32 bit limitation only 4 GB of the memory can be addressed per core. A mechanism referred to as *lookup table* (LUT) maps every core's physical 4 GB address space to the system's up to 64 GB of extended memory. There is one LUT per core. Each one contains 256 entries, which map memory segments of 16 MB size to the corresponding address in the core's address space. Possible memory locations for mapping are the private memory, local memory buffers, configuration registers, the system interface, power controller, and system memory. The LUTs can be dynamically reconfigured at runtime, what is especially interesting for possible implementations of shared virtual memory. Every tile also has a small amount (16 kB) of additional memory, namely the *message passing buffer* (MPB). This fast on-die memory can be used for more efficient communication between the cores, as classic architectures usually

Figure 2.1.: Schematic top view SCC block diagram

only provide the relatively slow off-die memory for this purpose [10].

The idea to provide shared virtual memory on message passing architectures has already been realized in clusters before. Previous approaches are, for example, *Treadmarks* [2], *ScaleMP* [1], *Cluster OpenMP* [8], and *vNUMA* [3]. These differ in various aspects: Some of them use virtualization to provide a transparent memory space spanning over the cores/nodes in a cluster, others provide this functionality on user space level. The majority of projects tried to establish shared virtual memory on non-uniform memory access platforms. Those platforms are adversely affected by communication latency, which is problematic in situations with dynamically changing memory access patterns and excessive synchronizing with locks. Finally, all approaches have proven to be extremely sensitive to network latency and suffered from lacking programming standards [6].

The SCC with its potential for low-latency-communication and uniform memory access characteristics offers the possibility to try this concept without the limitations, which are represented by latency and data locality on non-uniform memory access platforms. Furthermore, its special registers enable for optimizing the lock synchronization between cores. MetalSVM is specially suited for fast low-latency inter-core communication exploiting the SCC's message passing buffers. The establishment of shared virtual memory between the 48 cores is currently in development. With a virtualization layer the MetalSVM cores will be able to cooperate together hosting a single Linux kernel. Using virtualization, cores could even be multiplexed or turned off completely for saving energy. Another feature is the planned virtualization of I/O - presented solutions merely virtualized the memory. The Linux kernel will be able to manage the SCC's resources, just like it would on an ordinary SMP architecture. Cache coherence will then be achieved by software [13].

# 3. Hypervisors in Virtualization

This chapter explains virtualization and describes the role of the hypervisor within the virtualization of a computer system. After that, the Intel x86 architecture is considered as the virtualization platform to compare two different virtualization approaches and their adequacy for this project. At last different Linux hypervisors are introduced, outlining the choice for implementing lguest in MetalSVM.

**Definition 1 (Computer Virtualization)** Virtualizing a computer means creating virtual instances of its hardware which do not physically exist.

All applications running on such a virtual computer system must run with the identical effect as if they were running on a real machine. In this case, the virtualizing machine is also called *host machine*, while the virtual computer system is the *guest machine*. The program running on the host machine which is creating the virtual computer system environment is referred to as the *virtual machine monitor* (VMM) or *hypervisor*.

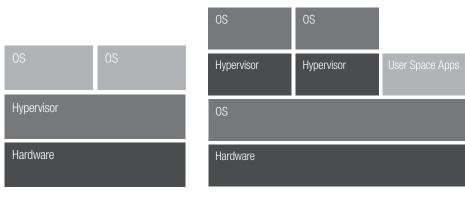

In 1973, Robert P. Goldberg distinguished between two types of hypervisors [5]:

**Type I** Bare metal hypervisor (Examples: Xen, KVM, lguest)

**Type II** Extended host hypervisor running under the host operating system (Examples: QEMU, Bochs)

(a) Type I hypervisors

(b) Type II hypervisors

Figure 3.1.: The two different types of hypervisors

#### 3. Hypervisors in Virtualization

Type I hypervisors run the virtual machines directly on the hardware. The examples Xen, KVM and lguest do virtualization within kernel space with highest processor privileges. KVM and lguest consist of kernel modules and a user space program [11] [15]. Xen is different and matches the Type I model more obviously: It provides a virtualization layer directly running on the bare metal machine (see also Figure 3.3 on page 11). Even the operating system instance which is used to manage the virtual machine configuration is being run as a guest [19]. This kind of hypervisor is often used in mainframe systems when the real machine is not used for anything else than virtualizing its guests to achieve high performance. Production applications will then be run on the guest machines.

Type II hypervisors are just user space applications being run on the host operating system. They are used when efficiency is only a minor constraint, but can be more flexible by being able to emulate a different processor/computer architecture for example. The lack of efficiency comes from emulating every instruction in software step by step [7].

Performance is an important constraint for this project. Thus, in the following Type II hypervisors will not be minded. The next section analyzes performance aspects of two different methods of Type I hypervisors to find the most suitable kind of hypervisor.

### 3.1. Full Virtualization Versus Paravirtualization

The traditional idea of virtual machine monitors provides an architecture completely identical to the model architecture being virtualized. This method is called *full virtualization*. On the one hand the guest operating system will then be able to run within this environment without the need for modification, but on the other hand this brings much overhead: Because the performance-aware user does not want to emulate every instruction in software, as much instructions as possible should be directly executed on the hardware. The problem here is that many computer architectures' design-goals did not imply virtualization. Operating systems designed for those will usually need to execute a certain set of privileged operations during normal operation. Those have to be *trapped and emulated* in software by the hypervisor. Especially Intel's x86 architecture fits into this group of architectures [14].

Trapping and emulating means switching back from the guest context to the hypervisor whenever the guest tried to execute an instruction which involves privileges it does not have. In general, the hypervisor does not know when and which privileged instructions occur in the future. Therefore, it depends on the programmer to find out how the architecture allows for stopping the guest's execution in the right moment. On some architectures this can end up in complicated workarounds and surely will slow down execution speed.

If the guest operating system can be modified to improve the performance, it can be called into question if it is still necessary to virtualize the whole architecture completely. The *Denali isolation kernel* for example was one of the first VMM

| Full Virtualization                                              | Paravirtualization                                                    |

|------------------------------------------------------------------|-----------------------------------------------------------------------|

| no change in guest OS                                            | guest OS must be ported                                               |

| slow due to trap & emulate overhead                              | fast - no instruction trapping & emulation                            |

| complex emulation of real hardware                               | simple & fast virtual device interfaces<br>establishing (VirtIO [16]) |

| operating from user space without<br>privileges (mainly Type II) | embedded into kernel (Type I)                                         |

Table 3.1.: Comparison between full- and paravirtualization

designs with the creation of a more abstract, but still x86-based architecture in mind. The guest kernel did not have to be compiled with special compilers, as it was developed for the x86 architecture instruction set, but it did not contain any privileged operation instruction calls either. This way the hypervisor's overhead of trapping and emulating in software was reduced significantly. The lack of privileged instruction set use was achieved by letting the guest kernel know it is a guest and make it call the hypervisor whenever it needs a privileged operation to be performed.

One important kind of and good example for privileged operation is hardware I/O: A dominant cause for traps and software emulation can be credited against emulating hardware devices. For this purpose Whitaker et al. designed simple hardware device abstractions of their physical counterparts: Drivers for such virtual devices can be split into frontend and backend parts. The frontend part lies within the guest kernel and uses buffers to communicate with the backend driver, which is managed by the hypervisor. Whenever hardware I/O is needed the guest kernel fills the device buffer and issues one single hypervisor call. The overhead of executing a sequence of I/O-instructions which would have to be emulated step by step can be avoided this way. Privileged operations and the overhead of their emulation are therefore kept out of the VMM implementation.

This method is called *paravirtualization* [18] [17]. A summarized comparison between full virtualization and paravirtualization is found in Table 3.1. Calls of a paravirtualized guest operating system to its hypervisor are referred to as *hypercalls*. For every privileged action, one special hypercall must exist. This is part of the common interface host and guest must implement.

The next section reveals in more detail why Intel's x86 architecture is complicated to virtualize. Furthermore it exemplifies where in the application flow paravirtualization achieves reduction of both overhead and complexity within the hypervisor by modifying the guest.

### 3.2. Virtualizing the Intel x86 Architecture

It was already hinted at before, that the Intel x86 architecture is notoriously difficult to virtualize due to its design lacking focus on virtualization. The problems which need to be solved by a hypervisor on this architecture are listed here.

All assumptions about the difficulty of virtualizing x86 processors are not true for current generations due to their support of new techniques for native *hardware virtualization*: With *Intel VT* and *AMD-V*, system programmers have the possibility to run guests within a hardware-provided virtual environment with several overheadlowering advantages [4]. This thesis covers virtualization mainly for the Intel SCC processor. The SCC's cores originate from the Intel P54C architecture which is too old to support hardware virtualization features. Therefore, these will be ignored here.

The following subsections describe typical x86-mechanisms which need to be handled by the running operating system. A guest operating system also has to handle them, but should not be allowed to access the corresponding instruction calls. After considering the costs of trapping and emulating all of them, it becomes clear why paravirtualization and the guest's virtualization-awareness allow for very much optimization. Instead of trapping every single privileged instruction the guest executes, it is possible to bundle everything what needs to be accomplished by the corresponding code section into one hypervisor call. The following information has been gathered from Intel's official software developer's manual [9] and J. Robin's and C. Irvine's analysis of the Intel Pentium as a virtualization platform [14].

#### 3.2.1. Segmentation

A more traditional approach than *paging* (virtual memory) to organize physical memory distribution and access privileges of multiple processes on the x86 platform is *segmentation*. Segmentation enables isolating code, data and stack areas per process from each other. Segments define offset and range within memory space, privilege level, etc. Still until today, the use of paging on 32 bit x86 CPUs is optional – segmentation is not.

So, even with a paging-enabled flat address space the code-, data- and stack segment registers have to be set properly at any time. The code segment, for example, is used by the processor to check if a process is allowed to continue if it tries to use privileged instructions.

Each segment is addressed by an index number in a descriptor table listing all available segments - the *Global Descriptor Table* (GDT). Before a segment is used it has to be described in the GDT. Loading/Storing the GDT with the instructions "sgdt" and "lgdt" demands operating at the highest privilege level. A guest machine must not be allowed to edit entries in the GDT itself directly, because this could be exploited for reaching a higher privilege level. There is also a *Local Descriptor Table* (LDT) for thread-local segments. Thus any access to GDT/LDT needs to be trapped and emulated, what is slowing down execution speed.

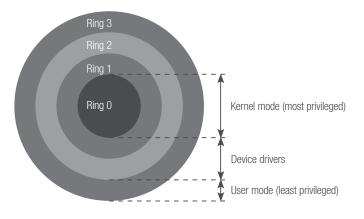

Figure 3.2.: Privilege rings in the Intel x86 architecture

#### 3.2.2. Privilege Levels, Rings

The x86 platform partitions privileges to four levels, numbered from 0 to 3. Level 0 stands for the highest privilege level — 3 for the lowest. On Intel CPUs, privilege levels are referred to as *rings* (see Figure 3.2). Usually, the operating system kernel's stack-, data- and code segment use privilege level 0 while user space applications use level 3 for each segment. The segment's descriptor denotes the *descriptor privilege level* number its owners obtain after loading it into a segment register. Loading a segment with a specified descriptor privilege level requires a certain minimum privilege level.

Of course one will not want to let the guest operating system run in ring 0. Most hypervisors choose ring 1 for their guests to enable automatic trapping on privileged operations. The hypervisor must keep track of the segment descriptors to be able to secure ring 0 from the guest. Having trapped a guest which tried to manipulate a segment descriptor, the hypervisor will need to check if the lowest privilege number the guest assigns to its own segment descriptors is equal or above 1.

#### 3.2.3. Virtual Memory

Virtual memory/paging involves the CPU using specific data structures maintained by the operating system. The architecture provides special registers (CR0 - CR4) for this purpose.

Again, access to this registers is restricted and must be trapped and emulated slowing down the virtual machine's execution speed. However, the whole page tree structure exposed to the MMU needs to be maintained separated from the guest's page tree. The guest's page tree should be considered unsafe as the guest must be prevented from ever mapping host memory to its address space. The guest could otherwise exploit paging to gain full access to the host system.

#### 3.2.4. I/O Operations

The guest should not be allowed to do any I/O operations on the hardware directly and should rather operate on virtual devices. Therefore the hypervisor must trap any I/O access and either simulate the non-existence of I/O devices or emulate virtual ones. The latter method means the overhead of a full software implementation of the according hardware interface.

#### 3.2.5. Interrupt Virtualization

As the guest should not have control over all interrupts, both *Interrupt Descriptor Table* (IDT) and *EFLAGS* register (manipulated by the "pushf", "popf", "cli" and "sti" instructions) need to be isolated from its access.

Manipulation attempts on the IDT and instructions manipulating the EFLAGS register therefore need to be trapped. Interrupts can be delivered to the guest by setting it into an interrupt situation with preconfigured stack- and segment configuration. This conserves the hypervisor's control, but slows down each interrupt.

Optimization can still be accomplished by delivering interrupts from the hardware directly into the guest without waking the hypervisor. It is important that the hypervisor ensures safe conditions when it installs the according IDT entry.

## 3.3. Hypervisors in Linux

The first free type I hypervisor implemented for Linux was Xen, released in october 2003 at Cambridge.<sup>1</sup> It supports both full virtualization and paravirtualizion. Xen matches the type I hypervisor definition very well: It implements a layer running directly on the hardware and thus it is positioned even beneath the operating system which is used for administration of the virtual machines [19].

Another virtualization solution for Linux is KVM ("Kernel-based Virtual Machine") which was released in October 2006. Also being a type I hypervisor, it does not match the type I definition as clearly as Xen. There is no *KVM layer* below the host operating system. KVM VMs will be run within an instance of QEMU utilizing a KVM Linux kernel module. This way, execution speed and privilege critical parts of the VM can be run on the bare metal machine by the host kernel [11].

The simplicity of loading a single set of modules (KVM) instead of reconfiguring the whole system to support virtualization (Xen) caused KVM's popularity to raise over Xen's.

Guest Linux kernels running under both hypervisors need to reimplement privilegecritical kernel functions to use hypercalls to delegate privileged tasks to the hypervisor. On the Kernel Summit in  $2006^2$  (still before KVM was published), Paul Russell (known under the name of *Rusty* Russel) proposed a simple solution to unify

<sup>&</sup>lt;sup>1</sup>Official announcement: http://sourceforge.net/mailarchive/message.php?msg\_id= 5533663

<sup>&</sup>lt;sup>2</sup>http://lwn.net/Articles/191923/

Figure 3.3.: Structural differences between the Xen and KVM hypervisors

the paravirtualization interface in Linux as a guest-side kernel: A structure called paravirt\_ops embodying a set of function call pointers to system-critical functions.<sup>3</sup> Those can be configured at boot time after detection of the right hypervisor to match its interface. This way the same kernel can run on a real machine or on one of the supported hypervisors without recompiling, which until today are Xen, KVM, VMWare's VMI and *lguest* [12].

#### 3.3.1. Lguest

Lguest is somewhat different compared to the other hypervisors. Rusty Russell wrote it at first to show how simple and useful his paravirt\_ops proposal is. In the end it turned out to be a complete hypervisor with I/O-drivers for block devices and network. Without features besides the core functionality of a hypervisor and implemented with just about 5 000 lines of code, it is quite spartan. Just like KVM, it brings its own Linux kernel module and guest kernel loader terminal application. It is very limited due to its lacking support for SMP at guest side, 64 bit kernels and suspend/resume features. Nevertheless it will run on virtually any x86 CPU because it does not depend on Intel VT or AMD-V – KVM does [15].

Another simplicity-enabling design choice of lguest is its lack of an *application binary interface* (ABI): It was not developed around a bold and complicated interface, whereas ABIs define strict and extensive conventions like data types, sizes and alignments. This makes lguest perfect for experimenting.

Being a 32 bit architecture and not providing Intel VT extensions, the Intel SCC perfectly matches into lguest's set of target platforms. Also, due to its simplicity and comfortably modifiable design, it was chosen as the right hypervisor for being ported to MetalSVM.

<sup>&</sup>lt;sup>3</sup>Introduced by patch: https://github.com/torvalds/linux/commit/d3561b7

# 4. Design and Implementation of the Hypervisor for MetalSVM

Lguest's implementation in MetalSVM is very similar to the original implementation in Linux. This chapter explains the implementation in the MetalSVM kernel and outlines structural differences to the Linux kernel. Lguest does in general consist of five parts – namely the context switcher, the user space loader application, the general hypervisor module itself, the **paravirt\_ops** structure, and VirtIO front- and backend drivers.

The hypervisor module embodies the host's functionality to maintain the virtualization environment for the guest kernel. Both host and guest share the *context switcher* code page which manages the change between their execution contexts. Implementing the paravirtualization interface between host and guest, the **paravirt\_ops** structure and the functions/procedures it points to are located in the guest kernel. Device driver I/O is implemented at host and guest side in the backend and frontend part of the VirtIO driver implementation. Finally, the virtualization functionality is provided to the user via the user space *loader application*. Table 4.1 gives a brief picture of which part of the code is executed at host or guest side:

| Host side             | Guest side             |  |  |  |  |

|-----------------------|------------------------|--|--|--|--|

| Context               | Switcher               |  |  |  |  |

| User Space Loader     | paravirt_ops           |  |  |  |  |

| Hypervisor module     |                        |  |  |  |  |

| VirtIO backend driver | VirtIO frontend driver |  |  |  |  |

Table 4.1.: Lguest's main parts

Context switcher and loader will be explained in their own sections later. The Hypervisor module is more complex and is split into several sections, while more general explanations will be found here.

To make clear how the parts work together, the application flow starting with the boot of the real machine will be described in sequential order until the guest operating system shell is started:

- 1. The reset pin of the real machine is released.

- 2. MetalSVM starts booting.

#### 4. Design and Implementation of the Hypervisor for MetalSVM

- 3. MetalSVM initializes the whole system and calls lguest\_core\_init()<sup>1</sup> at last.

- 4. The lguest initialization call creates a character device at /dev/lguest in the file system tree.

- 5. The host system is initialized and user space applications will be started now.

- 6. Lguest\_loader is the user space application which does the virtualization in cooperation with the MetalSVM kernel.

- 7. After lguest\_loader initialized the virtual memory environment for the guest, it informs the MetalSVM kernel using the /dev/lguest interface.

- 8. Kernel side initialization for the new guest is done.

- 9. Lguest\_loader will now enter its main loop where it reads from /dev/lguest and handles its output continuously. (see Figure 4.4 on page 23)

- 10. The virtualization itself happens in kernel space during each read(/dev/lguest) call: In general, the hypervisor switches to guest execution and handles interrupts and other events afterwards. This is done in a loop which is explained in the following.

- 11. The read() system call returns whenever any virtual device I/O (VirtIO) needs to be processed. System crashes and shutdowns also end up this way.

The virtualization loop in kernel space within run\_guest() (see Listing B.1) mentioned in step 10 is visualized in Figure 4.1. Rectangles with rounded corners denote actions on which run\_guest() either breaks out of the loop to return to user space, or to stop execution.

- lguest\_arch\_run\_guest()<sup>2</sup> performs the context switch to the guest system. Any interrupts must be disabled before entering.

- Whenever an interrupt occurs lguest\_arch\_run\_guest() returns. Traps will be processed in lguest\_arch\_handle\_trap()<sup>2</sup>, interrupts have to be delivered to the guest at the next context switch.

- Hypercalls are processed by do\_hypercalls()<sup>3</sup>. As it is possible to bundle multiple asynchronous hypercalls within a list, they will be processed in a loop.

- A *notify* event occurs on virtual guest device I/O. In this situation **run\_guest()** returns back to user space, as the backend drivers are not implemented in the kernel.

$<sup>^1\</sup>rm defined$  in metalsvm/drivers/lguest/lguest\_core.c

$<sup>^2\</sup>mathrm{defined}$  in metalsvm/drivers/lguest/x86/core.c

$<sup>^{3}</sup>$  defined in metalsvm/drivers/lguest/hypercalls.c

- If the last interrupt stopping the guest machine was an interrupt which should be delivered back to it, this will be done just before entering the guest again: The interrupt can be delivered by forming the guest stack just like it would look in case of a real interrupt.

- Another cause to return to user space are cases which cause the guest machine to stop like crashes, shutdowns, and reboot attempts.

- The virtualization process can be made subject to being rescheduled, if the guest halts in inactivity waiting for further interrupts, unless there are interrupts waiting to be delivered.

Figure 4.1.: Flow of Iguest's main loop

## 4.1. Hypervisor Initialization

Before being able to provide a virtualization interface for the user space guest loader, some initialization in the MetalSVM kernel is done at boot time. Just like UNIX operating systems do, MetalSVM provides a /dev directory in the filesystem where it keeps user space accessible files representing devices. The corresponding lguest-file is a character device both accepting and emitting character streams called /dev/lguest. This is done in the lguest core init()<sup>4</sup> procedure.

The whole initialization process consists of 4 parts:

- 1. Loading the switcher pages

- 2. Initializing the part of the pagetables every guest initially uses

- 3. Creating the character device file /dev/lguest in the file system

- 4. Initializing architecture-specific data structures of both host and future guests

#### 4.1.1. Loading the Switcher Pages

The *switcher pages* area in the host's and guest's memory space consists of three pages: One page containing the actual code which manages the context switch between host and guest and two further pages which are for storing host and guest states. If the host is an SMP system, the both pages for storing host/guest states exist once per every CPU in the system, because multiple guests can be run at the same time.

Initializing those means allocating memory for an array keeping pointers to every page and for the pages themselves. The first allocated page is then used for containing the switcher code. It will be copied from where it is initially located in the kernel to the beginning of this page.

After that, the first switcher page containing the context switch instructions is mapped to SWITCHER\_ADDRESS on every cpu's address space. The per-CPUpages are mapped behind this first switcher page on the corresponding CPUs. SWITCHER\_ADDRESS is a constant value which is set to 0xFFC00000 in the most cases, but can be different. As those pages also will be mapped in the guest address space at the same address location, the very end of the 32 bit address space is an appropriate location.

### 4.1.2. Initializing Page Tables

Early at boot the guest kernel will be instructed not to use any page from between SWITCHER\_ADDRESS to the very end of the memory space. This leads to the same few last page directory entries in every guest space if several guests are running at the same time. The corresponding page tables are created now.

$<sup>^4\</sup>mathrm{defined}$  in metalsvm/drivers/lguest/lguest\_core.c

To secure the host state keeping memory structures while the CPU is operating in guest context, the switcher page containing the host state is mapped read-only in the guest's page tables. Of course the context switcher code page is mapped read-only, too. These page directory and page table entries will be shared between all guests. The guest kernels will not map their own pages into this area.

#### 4.1.3. Creating /dev/lguest in the Filesystem

MetalSVM provides functions and data structure definitions to enable the abstraction of system functions to file system I/O character streams. Therefore the /dev filesystem node is found by using finddir\_fs(fs\_root, "dev") and then a new node with the filename lguest is initialized and installed within the former one.

The special attributes of this file system node are its *character device* type and the corresponding pointers to functions for the system calls open(), close(), read() and write(). Utilizing these, lguest provides the interface for communication with its user space application.

#### 4.1.4. Architecture-Specific Initialization

The initial interrupt descriptor table of all guests is the same. Before being ready to use, the interrupt handler's address pointers within every entry need to be relocated with the offset of the actual switcher page address.

Afterwards, the IDT, GDT and Task State Segment (TSS) descriptors are set up to values which are the same for every initial guest. The TSS contains a bitmap denoting which I/O ports the corresponding running process is allowed to use. This bitmap's fields are all set to a value representing the meaning "*none*", because the guest must not do any I/O by itself.

While switching the context and generally later in guest kernel space, host/guest kernels use the same segment numbers for their code and data segment (notably LGUEST\_CS and LGUEST\_DS). Their descriptors are configured with the usual flags corresponding to code/data segments, but the guest version of those is not configured to make the CPU operate on privilege ring 0, of course. These descriptors are configured here and the host version is installed into the host GDT.

Every context switch from host to guest will be started with an lcall instruction later. As the only parameter to this instruction is a structure keeping the target code's address offset and segment, this structure is initialized now to the switcher code address and LGUEST\_CS segment.

Figure 4.2.: Hypervisor-recognition at boot time

### 4.2. Guest Boot and paravirt\_ops

Of course, as in paravirtualization host and guest have to cooperate, the guest must know it is a guest running under control of a hypervisor instead of running alone on the bare metal system.

Early at boot, the Linux kernel will enter its startup\_32 routine<sup>5</sup>. It clears the uninitialized C variables by writing zeros over the whole *BSS* range. Then it moves the boot header structure (boot\_params) as well as the kernel command line string to another place in the memory. If paravirtualization guest support was enabled at compile time, it will then check the boot\_params structure's subarch field<sup>6</sup> (see Listing B.2).

If this field's value is 1<sup>7</sup> then it recognizes itself as a guest of the lguest hypervisor and calls lguest\_entry<sup>8</sup>. This procedure steps over the initialization of paging etc. since this is already done by the hypervisor (see Figure 4.2). The first thing to happen in lguest\_entry (see Listing B.3) is the initialization hypercall to the host. The only parameter is the address of the guest's lguest\_data structure. Now the host can initialize the guest's clock, frequency setting and inform the guest about its allowed memory dimensions by writing this information back into that structure.

Back in guest kernel space, the kernel reaches its first instructions generated of C-code while entering lguest\_init() (see Listing B.4).

The paravirt\_ops structures' function pointers are set to the right paravirtual-

<sup>&</sup>lt;sup>5</sup>defined in linux/arch/x86/boot/compressed/head\_32.S

<sup>&</sup>lt;sup>6</sup>Introduced by patch: https://github.com/torvalds/linux/commit/e5371ac

$<sup>^7</sup> Value~0$  stands for a normal PC architecture without any hypervisor, 2 stands for Xen  $^8 defined$  in linux/arch/x86/lguest/i386\_head.S

ization procedure calls. The kernel is now able to cooperate with its host and will not try to execute instructions which require a higher privilege level. Between some more hardware registration the virtual console device is registered and callbacks for crash situations and shutdown are set.

Now the  $i386\_start\_kernel()$ <sup>9</sup> procedure is called and the kernel finally continues executing its usual boot code.

<sup>&</sup>lt;sup>9</sup>defined in linux/arch/x86/kernel/head32.c

Figure 4.3.: Memory layout of host and guest

## 4.3. Lguest Loader

The whole virtualization is initiated by a simple user space process. In this implementation the program is called *lguest\_loader*. It takes the following command line parameters:

- Guest kernel image file system path

- The guest's initial ramdisk image file system path

- The guest's physical memory size

- Guest kernel command line parameters (optional)

Subsequently, it will allocate the guest's later physical memory using malloc(): This sector's size is the size parameter the user provided plus the *device pages* (default constant value is 256 pages) size. This area needs to be aligned to page boundaries. In the following, the address of the beginning of this area will be denoted by guest\_base and the size of this area without the device pages by guest\_limit (see Figure 4.3).

For the user space process the guest's physical address space is just this linear range. Hence, to calculate from host-virtual to guest-physical addresses it is only required to subtract guest\_base—or to add this value to convert a guest-physical address to host-virtual.

Loading the kernel image file is a straightforward process: At first, the file is checked for *magic strings* indicating it is an *ELF* file, then its *ELF-header* is checked. Finally, the *ELF load sections* are loaded to the proper positions in the guest-physical memory. The initial ramdisk is loaded to the end of the guest's memory area.

#### 4. Design and Implementation of the Hypervisor for MetalSVM

At current development state, the loader only implements a virtual console device which is initialized then. Due to the complexity of the *VirtIO* interface, details on the interface itself will be explained later. The virtual interfaces utilize buffers which need to be mapped at host- and guest-side. The function get\_pages() obtains memory for this buffers by pushing the guest\_limit border deeper into the VirtIO device pages area.

The last step before telling the hypervisor about the guest is providing a proper **boot\_params** structure. This structure is placed at guest-physical address 0 and contains the following information:

- An e820 memory map with an entry specifying the guest's physical memory size

- A pointer to the kernel's command line parameters (which are copied into the guest memory just behind the boot\_params structure)

- If provided, the initial ramdisk image's position and size

- The hardware\_subarch field (as already described in the section before) is set to 1 (Indicating the presence of the lguest-hypervisor). Early at boot time, the guest kernel will check this value and recognize that it is running under a hypervisor

- There is also a variable loadflags where the KEEP\_SEGMENTS flag is enabled to hold the booting kernel off reloading the segment registers since the hypervisor will have it set properly already

Telling the hypervisor about the new guest is done by writing information to the /dev/lguest file: This information consists of 16 bytes which contain the following:

- an enumeration value LHREQ\_INITIALIZE to denote the format of the next written bytes

- the host-virtual guest\_base address

- the number of pages between guest\_base and guest\_limit

- the guest-physical start address of the kernel executable.

In the meantime, in kernel space, the hypervisor allocates all structures it needs to manage the guest and initializes the guest's registers (by choosing the right segments, EFLAGS, instruction pointer, etc.), its GDT and initial page mapping in the shadow pages. Before boot, the initial page mapping contains identity mapping for all guest-physical pages. Linux kernel space mappings begin at an offset of PAGE\_OFFSET which in x86 is at address 0xC0000000 and are initially mapped to page frames 0 and following. The *switcher pages* (see Figure 4.3) are mapped at the same address as in the host.

Figure 4.4.: Flow of Iguest\_loader's main loop

After returning to user space from the write() call to /dev/lguest everything is ready to start the guest machine. Lguest\_loader will now enter its run\_guest() procedure which merely contains an infinite loop where a read() call on /dev/lguest and processing code for its output is located. (see Figure 4.4)

For the whole lifetime of the guest system, the virtualization will take place while lguest\_loader is blocking on the read() call. This call returns to user space whenever critical error messages or virtual device events for device output occur or if the guest just wants to shut down or reboot. The guest kernel also emits boot messages this way before its virtual console is initialized.

### 4.4. Host-Guest Context Switch

Switching the context from host to guest and back requires saving all register states of one machine and restoring the state of the other machine. On the x86 architecture this also involves loading the right segments, a different GDT, IDT and TSS as well as switching the MMU to another page tree. In the end the whole context switching procedure should also be NMI-safe. The code which manages this task is usually mapped to address 0xFFC00000, because this way the last page directory entry can be used for the switcher code and the state structures of host and guest. The Linux kernel does also have an internal variable \_\_FIXADDR\_TOP which is used to specify the last mappable virtual address. Both Linux host and guest kernels do this to protect this area. Due to architectural restrictions, MetalSVM uses address 0xFF800000.

To switch from host to guest, the hypervisor just needs to call the run\_guest\_once() procedure (see Listing 4.1) which first calls copy\_in\_guest\_info() to copy the guest state information into a data structure mapped just behind the switcher page. Every core on the system has its own structure of this kind. On single core systems this is rather uninteresting, as this procedure does only copy conditionally: Either if a different guest than before is run on the same core or if a guest is moved to another core.

```

1

static void run_guest_once(struct lg_cpu *cpu, struct lguest_pages *pages)

\mathbf{2}

{

3

unsigned int clobber:

4

/* Copy over guest-specific data into this cpu's struct lguest_pages */

5

6

copy_in_guest_info(cpu, pages);

7

8

/* Set trapnum to impossible value. In case of NMI while switching

9

* this will help to identify the situation */

10

cpu->regs->trapnum = 256;

11

12

asm volatile("pushf; _lcall_*lguest_entry"

: "=a" (clobber), "=b" (clobber)

13

/* EAX contains the pages pointer,

14

15

* EBX contains physical address of guest's page directory */

16

: "0" (pages),

"1" ( cpu->lg->pgdirs[cpu->cpu_pgd].pgdir)

17

18

: "memory", "%edx", "%ecx", "%edi", "%esi");

19

7

```

Listing 4.1: run\_guest\_once() procedure (metalsvm/drivers/lguest/x86/core.c)

The trapnum variable within the core's regs structure (line 10 in the code listing) is used to save the last interrupt number from which the guest was interrupted. A value of 256 is impossible, because the x86 only allows for numbers 0 to 255. This is used to detect NMIs which occured during the context switch: If an NMI occurs, the machine will immediately switch back just like on any other interrupt. After returning from run\_guest\_once() the hypervisor will call lguest\_arch\_handle\_trap() which will detect the NMI and drop it. It is unlikely that the next host-guest switch

fails, too.

Finally, in line 12 of the code listing, the switcher code itself is called. The *eax* register is set to the current core's **struct lguest\_pages**'s address and *ebx* is set to the guest's page directory address. **lguest\_entry** is a structure containing the switcher code's entry offset and the segment selector LGUEST\_CS the code shall be executed on. Now, the **switch\_to\_guest** assembler routine (see Listing 4.2) which just has been called shall be regarded line by line:

- Lines 3f push the host's segment registers and frame pointer onto the stack. They will be popped back when returning to the host.

- Lines 10f The task state segment register must be pushed onto the stack. Linux' original lguest implementation does not need to do this, because the Linux kernel uses only one task state segment per core. MetalSVM utilizes hardware task switching, therefore this TSS's descriptor number can be one of several possible ones and needs to be saved.

- Line 13 The host's stack pointer is saved in the lguest\_pages structure.

- Lines 15f As *eax* contains the struct lguest\_pages' address, it is only necessary to add the offset that the regs field has within the struct to get the address of the guest's set of registers. The stack pointer is set to this address this way the guest stack instead of the host stack is modified by a possibly occuring NMI.

- Lines 19f load GDT and IDT register values from lguest\_pages.

- Lines 23f The guest's TSS register must be loaded before switching the CR3 register to the shadow page tree. Intel x86 CPUs alter the TSS descriptor by setting a *used-bit* after loading with the "ltr" instruction. To protect from loading a TSS twice, issuing the "ltr" instruction on a TSS with a used-bit, which is already set, provokes a general protection fault. Therefore, this change in the host's TSS has to be reverted immediately. After changing the CR3 register to the shadow page trees, the struct\_page which has been used to save the host's state is only mapped read-only to isolate host from guest. The used-bit of the previous TSS is not changed automatically by issuing the "ltr" instruction - it is more common to switch TSS registers at a task switch with a far jump denoting both the next task's instruction pointer and its TSS. This is not possible at this point.

- **Lines 26f** load the host-GDT address into the *edx* register. So, edx + ecx + 5 is the address of byte 5 in the host's TSS descriptor, where bit 2 is the *used-bit* which needs to be cleared.

- Line 29 loads the shadow page tree address into the CR3 register. Now the page with the host state structure is mapped read-only and the guest cannot harm it.

#### 4. Design and Implementation of the Hypervisor for MetalSVM

**Lines 31f** All the guest registers are simply popped off the stack.

- Line 43 steps over the trapnum and errcode fields in the lguest\_regs structure. These fields are needed elsewhere to save interrupt number and error code before switching back to the host.

- Line 45 Entering the guest code looks like returning from an interrupt. Finally, the context switch is complete.

```

1

ENTRY(switch_to_guest)

2

3

pushl

%ss

4

pushl

%es

5

%ds

pushl

pushl

6

%gs

pushl

7

%fs

8

pushl

%ebp

9

10

%ecx

str

11

pushl

%ecx

12

13

movl

%esp, LGUEST_PAGES_host_sp(%eax)

14

15

movl

%eax, %edx

$LGUEST_PAGES_regs, %edx

16

addl

17

movl

%edx, %esp

18

LGUEST_PAGES_guest_gdt_desc(%eax)

19

lgdt

20

21

lidt

LGUEST_PAGES_guest_idt_desc(%eax)

22

23

movl

$(GDT_ENTRY_TSS*8), %edx

24

ltr

%dx

25

26

(LGUEST_PAGES_host_gdt_desc+2)(%eax), %edx

movl

27

$0xFD, 0x5(%edx, %ecx)

\texttt{andb}

28

29

%ebx, %cr3

movl

30

31

%eax

popl

32

popl

%ebx

33

%ecx

popl

34

%edx

popl

35

popl

%esi

36

popl

%edi

37

popl

%ebp

38

popl

%gs

39

%fs

popl

40

%ds

popl

41

popl

%es

42

43

addl

$8, %esp

44

45

iret

```

Listing 4.2: Host-guest switcher code (metalsvm/drivers/lguest/x86/switcher\_32.S)

Switching back from guest to host is very similar, hence not explained here except for a detail: Ensuring to find the address of the host's state structure within

struct lguest\_pages. This must success even if an interrupt occurs while restoring the guest's registers within the switch process from host to guest. This situation is tricky:

Listing 4.3 shows the definition of struct lguest\_pages and two assembler lines extracted from the routine which switches back from guest to host. Whenever an interrupt occurs at guest's side the TSS sets the stack pointer back to within struct lguest\_regs in struct lguest\_pages. This way, trap number, error code and registers are automatically saved into the lguest\_regs structure by the CPU. Now it is a crucial task to find the read-only host state structure to restore the host context. The only hint lies within the stack pointer: As it was set to the last ring 0 stack position in struct lguest\_regs by the TSS, it is only a matter of offset-calculation to find the read-only host state structure.

The only problem left is that it is not safe to assume that the stack has the same well-defined height on every context switch back to the host. If a fault occurs while the guest registers are popped off the stack while switching from host to guest, a simple offset-calculation to find the read-only host state structure will not work out any longer. This problem is solved by aligning struct lguest\_pages at pageboundary and putting its struct lguest\_regs to the very end of the first page it occupies. The space between is filled with spare bytes. With this layout, the stack pointer's lowest 12 bits can be just cleared out to obtain the lguest\_page's base address (see the assembler code in the listing). Using this as base address, simple offset calculations can be applied again to find the read-only host state structure.

Combined with comprehension of this detail the rest of the context switch code switching back to the host is finally analogous to the switch from host to guest.

```

/* lguest.h */

1

struct lguest_pages {

2

3

/* This is the stack page mapped rw in guest */

char spare[PAGE_SIZE - sizeof(struct lguest_regs)];

4

5

struct lguest_regs regs;

6

/* This is the host state & guest descriptor page, ro in guest */

7

8

struct lguest_ro_state state;

9

} __attribute__((aligned(PAGE_SIZE)));

10

11

switcher_32.S */

12

/* ... */

movl

%esp, %eax

13

14

andl

$(~(1 << PAGE_SHIFT - 1)), %eax

15

/* ... */

```

Listing 4.3: Definition of the lguest\_pages structure and restoring the stack pointer during guest-host context switch

## 4.5. Segments

Segments are the heart of lguest's guest-isolation functionality, because the loaded code segment defines at which privilege level the CPU is currently running on. It is very important to keep track on the changes the guest tries to write to the global descriptor table. If necessary the hypervisor needs to reject or alter them to hold the guest off from obtaining the host's privilege level.

The highest privilege level the guest can obtain during its lifetime is the ring 1 privilege level. To achieve this, the guest's kernel space code and data segments have to be manipulated. These and the task switch segment (TSS) as well as the doublefault TSS need to be secured from any write-access by the guest.

## 4.5.1. Special Segments for the Guest's Kernel Space

Most important for kernel space are the LGUEST\_CS and LGUEST\_DS segments which are to be used by the code and data segment registers.

LGUEST\_CS's segment descriptor has the same flags like the KERNEL\_CS segment descriptor on which Linux kernel space code is usually running on. The only difference is the descriptor privilege level flag which is set to a value of 1 to let the guest run on ring 1. The same applies respectively for LGUEST\_DS and KERNEL\_DS, which is generally used for data-, extra- and stack-segment registers. The host kernel has its own versions of LGUEST\_CS and LGUEST\_DS with ring 0 set as descriptor privilege levels. These are loaded on entering the context switch code.

As the TSS preserves the old code segment and determines which segment shall be loaded to the stack-segment register etc., it is considered to be too powerful to be manipulated by the guest. The hypervisor ensures that it never switches the guest to ring 0.

## 4.5.2. Managing GDT Manipulation Requests

The guest has no write-access to the GDT because it is mapped read-only in its virtual address space. Therefore there are two hypercalls available for it to manipulate segment descriptors: LHCALL\_LOAD\_GDT\_ENTRY and LHCALL\_LOAD\_TLS.

LHCALL\_LOAD\_GDT\_ENTRY takes an 8 byte segment descriptor as parameter. The hypervisor will then install it into the GDT which is destined to be active while guest execution. Of course the hypervisor will not accept to install segment descriptors which could enable the guest in obtaining full privileges.

If the proposed segment descriptor would give the guest full privileges the hypervisor just overwrites the descriptor privilege field (DPL) with a value of 1 standing for ring 1. The *accessed-bit* within the descriptor's type field will be set by the hypervisor, too. If it is not set in the moment the guest tries to load the segment, the CPU would try to set it and fail, because it has insufficient privileges.

Mentioned fields the hypervisor changes within the segment descriptor are shown in Figure 4.5. There are four segment descriptors to which the guest has no access,

Figure 4.5.: Structure of a segment descriptor [9]

thus the hypervisor rejects any attempt to change them: The TSS, LGUEST\_CS, LGUEST\_DS and doublefault TSS segment descriptors.

LHCALL\_LOAD\_TLS is a hypercall for optimization, as the three thread-local storage segment descriptors need to be changed on every context switch and will be processed by the hypervisor in a row.

## 4.6. Interrupts

The guest machine depends on the interrupt and exception functionality of the CPU, just like any other machine. Of course, the host must stay in full control over the interrupt/exception mechanism at any time to ensure the system's security and integrity. Also, the host needs to be able to reschedule the guest's virtualization process to serve its other processes with CPU time equally well.

Initially, all interrupts/exceptions which occur while the guest is running cause a context switch back to the host. Depending on the kind of interrupt it is delivered to the host just as if it occured while the host was running. Exceptions are delivered to the hypervisor for further analysis. To enable this distinction, a special interrupt descriptor table is installed when switching the context to the guest: Its vector number entries point to three different handlers:

Vector numbers 0, 1, 3...31, 128 Most of these are architecturally defined exceptions, which are issued by the CPU if errors occur or special instructions are used. The operating system has to handle them to keep the ability to run properly. Handling these interrupts mostly involves the need for higher privileges. Thus, the interrupt/exception number is pushed onto the stack and delivered to the hypervisor.

Vector number 128 is typically used for system calls, which are issued by the guest's user space processes, so they should not be delivered to the host operating system but instead sent back to the guest.

- **Vector number 2** Used for Non-maskable interrupt: The handler for this does nothing else than returning to normal execution of the guest code.

- Vector number 32...127, 129...255 Being issued by some external cause or by software, interrupts assigned to vector numbers within this range need to be delivered to the host operating system and not the hypervisor code itself. For this purpose the context is switched back like usual, but in the following the host's IDT is searched for the current interrupt's IDT descriptor to jump to the right handler. After handling the interrupt the hypervisor continues execution on host side as if it returned from switching back from the guest as usual.

## 4.6.1. Managing IDT Manipulation Requests

The guest can issue an LHCALL\_LOAD\_IDT\_ENTRY hypercall to the host to tell where it wants an interrupt or exception to be delivered for handling. The hypervisor will then write the segment descriptor the guest provides into the guest-IDT. Before the hypervisor accepts a segment it checks some attributes and its privilege level:

• The guest is not allowed to change interrupt descriptors of the vector numbers 2, 8, 15 and LGUEST\_TRAP\_ENTRY (commonly 0x1f). These are for NMI, double

Figure 4.6.: Structure of an interrupt descriptor [9]

fault, the  $spurious interrupt^{10}$ , and lguest-Hypercall. The guest will never have to handle them by itself.

- Solely *interrupt-* and *trap-gate-*types are allowed as segment descriptors.

- Just in case the guest tries to install an interrupt descriptor with a privilege level lower than 1 (that means assigning a higher privilege than allowed to the interrupt handler) the hypervisor overwrites this flag to ring 1 priority.

All in all, the hypervisor copies only the interrupt handler's address, present-bit, privilege level and descriptor type into the IDT. Segment descriptors with an unset present-bit are zeroed out completely. As seen in Figure 4.6 the fields which are completely overwritten by the hypervisor are colored dark grey and the fields which are just checked are colored light grey.

## 4.6.2. Guest-Interrupt Handling in the Hypervisor

Immediately after every context switch back to the host, the hypervisor calls the procedure lguest\_arch\_handle\_trap()<sup>11</sup> to determine the kind of interrupt/exception which caused the guest execution to stop. This procedure does in general consist of one switch-case construct handling the following Intel-defined interrupt vector numbers:

Vector number 13 General protection fault - This can be caused by the following:

• I/O instructions - As Linux' paravirtualization structure is not absolutely complete, the guest tries to probe I/O ports at boot time. The hypervisor lets the guest just skip them and write return values to the guest's registers with all bits set which is the common value to signalize that this I/O port is not used.

$<sup>^{10}\</sup>mathrm{Spurious}$  interrupts do occur because of noise and other conditions. They are not supposed to need special handling.

$<sup>^{11}\</sup>mathrm{defined}$  in metalsvm/drivers/lguest/x86/core.c

- The vmcall instruction If the Intel VT extension is not available or available but not initialized (lguest does not support it, therefore it is not initialized), this instruction causes a general protection fault. It will be redirected to the exception 6 handler.

- If the general protection fault was not due one of the causes above it will be redirected to the guest later.

- Vector number 6 Invalid opcode If this exception was caused by a vmcall instruction this is either a rerouted vector number 13 or 6 on a CPU not supporting the Intel VT extension. In both cases the 3 bytes long instruction "vmcall" will be patched with another 3 bytes "int 0x1f; nop". In any other case it is delivered back to the guest later.

- **Vector number 7** Device not available fault This happens if a guest process tried to utilize the floating point unit. The hypervisor manages its register state storing and restoring.

- Vector number 14 Page fault The hypervisor will refresh the corresponding shadow page tree to fulfill the MMU's demand. If it cannot find a corresponding entry within the guest's page tables while it is trying to achieve this, the exception will be delivered to the guest which has to refresh its own page tree.

- **Vector number LGUEST\_TRAP\_ENTRY (0x1f)** Hypercall The guest issued a hypercall and its parameters lie within the processor's all-purpose registers which already have been saved in the guest processor state structure. The hypervisor sets a pointer to this structure of parameters which will be checked in its hypercall-processing section later.

If the hypervisor decides to send one of the interrupts/exceptions above back to the guest or an interrupt occured which has a vector number lower than 32 but not listed above, it will try to deliver it to the guest now.

## 4.6.3. Delivering Interrupts Back to the Guest

Interrupt delivery to the guest works by simulating the processor's real actions in the case of an interrupt/exception before letting the guest execute its code again. The hypervisor achieves this by forming the stack in the same way the processor does when it is interrupting the execution.

There are different cases and types of interrupt/exception which the stack has to reflect before calling the handler routine:

• It makes a difference on which privilege level the processor is running before it is being interrupted:

If it is running in kernel space, the processor will save the EFLAGS register, code segment and instruction pointer onto the stack and jump to the handler (see Figure 4.7(a)).

As user space processes do not have sufficient privileges to handle interrupts/exceptions, a privilege level switch to a higher privilege (lower ring number) is necessary<sup>12</sup>. The TSS arranges a switch of both the stack pointer and stack segment to the kernel stack. While the user space stack stays unchanged, the former user space stack segment and stack pointer are pushed onto the kernel stack. After this the same registers are pushed onto the stack just like in the kernel space interrupt case described before. (see Figure 4.7(b))

• Vector numbers 8, 10 to 14, and 17 are used for exceptions which supply error numbers. These are pushed onto the stack by the processor after saving the register states. The hypervisor has to distinguish if it needs to simulate this, too.

After handling, the stack's state will be rolled back to the state from before the interrupt has occured by using the **iret** instruction. It is the last instruction of every interrupt/exception handler in general.

Figure 4.7.: Stack layouts before and after the occurence of an interrupt

## 4.6.4. The Guest's Possibilities to Block Interrupts

Usually on the x86 architecture interrupts are enabled and disabled with the sti ("set interrupt-bit") and cli ("clear interrupt-bit") instructions. These instructions manipulate the EFLAGS register, thus require a privilege level the guest does not have.

The lguest-guest's interrupts are generally delivered to the host first. Therefore the guest can either tell the host to selectively disable the delivery of specific interrupts or to completely disable the delivery of interrupts at all. For this purpose

$<sup>^{12}{\</sup>rm The}$  privilege level during the interrupt is defined in the segment descriptor which is chosen by the interrupt descriptor

there is a field irq\_enabled and a bitmap field blocked\_interrupts within struct lguest\_data to which both host and guest have access.

The hypervisor uses the function interrupt\_pending()<sup>13</sup> to determine if there are interrupts to be delivered to the guest. Whenever an interrupt already has occured – and thus needs to be delivered to the guest – but its bit in blocked\_interrupts is set, it will be ignored. The delivery will take place later when the guest has cleared the block-bit again. If the irq\_enabled field's bit 8 is unset (which is also the interrupt-bit in the EFLAGS register) the function interrupt\_pending() will not return any interrupt vector number at all. The lguest Linux kernel provides its own procedures at guest side to replace the architecture-specific set/unset calls for the interrupt-bit. Selective interrupt control is abstracted behind a simple configurable lguest IRQ controller "chip" interface.